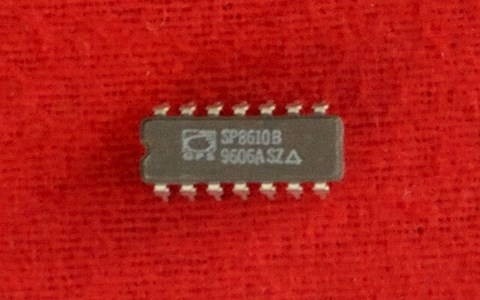

SP8610-11

Features

- ECL Compatible Outputs

- AC Coupled Input (internal bias)

- Input Frequency: 1500MHz (SP8611B)

Quick Reference Data

- Supply Voltage: -5.2V

- Power Consumption: 380mW

- Temperature Range: -55°C to +125°C (A Grade)

Description

The SP8610/11 are asynchronous ECL divide by four circuits, with ECL compatible outputs which can also be used to drive 100-ohm lines. They feature input sensitivities of 600mV p-p (800mV p-p above 1300MHz).

Operating Note

- The clock input (pin 4) should be capacitively coupled to the signal source. The input signal path is completed by connecting a capacitor from the internal bias decoupling, pin 6 to ground.

- If no signal is present the device will self-oscillate. If this is undesirable, it may be prevented by connecting a 10k resistor from the input to Vee (i.e. Pin 4 to Pin 7). This reduces sensitivity by approximately 100mV.

- The input can be operated at very low frequencies, but slew rate must be better than 200V/µs.

- The input impedance of the SP8610/11 is a function of frequency. See Fig. 4.

- The emitter follower outputs require external load resistors. These should not be less than 330 ohms, and a value of 430 ohms is recommended. Interfacing to ECL III/10K is shown in Fig. 7.

- These devices may be used with split supply lines and ground referenced input utilising the circuit of Fig. 6.